सॉकेटेबल चिपलेट: अपग्रेडेबल SoC का नया विचार

कंप्यूटर हार्डवेयर की एक अनजानी परत अब धीरे-धीरे सतह पर आ रही है, जहाँ छोटे चिप-सुचारू समाधान बड़े प्रदर्शन और ऊर्जा बचत का वादा करते हैं। यह कहानी उन नए मॉड्यूलरों, कस्टम ASICs और ऊर्जा-कुशल माइक्रो-नियमों की है जो सस्ते, तेज और टिकाऊ उपकरणों की दिशा बदल रहे हैं। छोटे स्टार्टअप से लेकर बड़े निर्माता बदलाव में हिस्सेदार बन रहे। यह लेख बताता है कि सॉकेटेबल चिपलेट क्या हैं, क्यों वे अब संभव हो गए हैं और वे उपयोगकर्ता अनुभव और बाजार को कैसे बदल सकते हैं। आगे हम इतिहास, वर्तमान प्रगति, कीमतें, चुनौतियाँ और संभावित परिणामों का विस्तृत विश्लेषण देंगे।

इतिहास और तकनीकी पृष्ठभूमि

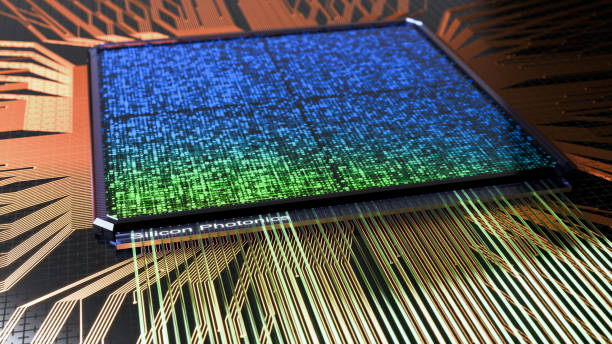

चिपलेट विचार नया नहीं है, लेकिन हाल के वर्षों में पैकेजिंग और इंटरकनेक्ट में आए बदलावों ने इसे व्यवहारिक बना दिया है। AMD ने 2019 में Zen 2 आर्किटेक्चर के साथ बहु-डाई डिजाइन को मुख्यधारा में लाया, जिसने दिखाया कि बड़े, हाई-परफॉर्मेंस प्रोसेसर को छोटे, अलग-अलग डाइ में विभाजित कर के लागत और पैदावार दोनों में लाभ मिलता है। Intel ने Foveros जैसी उच्च-स्तरीय 3D पैकेजिंग तकनीकों के साथ मल्टी-डाय स्टैकिंग को आगे बढ़ाया, और TSMC तथा अन्य फैब्स ने CoWoS और advanced packaging पर भारी निवेश किया। इन विकासों ने परंपरागत मोनोलिथिक SoC से हटकर बहु-डाई, मॉड्यूलर दृष्टिकोण को संभव बनाया, जिससे डिज़ाइन लचीलापन और तेजी से इन्नोवेशन हुआ।

अब क्यों संभव है: मानक, पैकेजिंग और आर्थिक कारण

हाल के सालों में दो चीज़ों ने इस बदलाव को तेज़ किया: एक है उन्नत पैकेजिंग और दूसरा है उद्योग-स्तरीय इंटरकनेक्ट मानक। बिल्डिंग-ब्लॉक्स के रूप में काम करने वाले छोटे चिपलेट को एप्लिकेशन-विशेष बनाना आसान हुआ है क्योंकि UCIe जैसे प्रयासों से दाइ-टू-डाइ इंटरकनेक्ट पर फोकस बढ़ा। इसके साथ ही फाब क्षमता, अलग-अलग नोड्स पर उत्पादन और परीक्षण की प्रक्रियाएँ सुधरी हैं, जिससे छोटे बैचों में भी आर्थिक रूप से उत्पादन संभव हुआ है। इसके अलावा, वैश्विक सप्लाई चेन में विविधता लाने के इच्छुक OEMs और ODMs के लिए चिपलेट मॉडल आकर्षक है क्योंकि वे विशिष्ट कार्यों के लिए अलग कारखानों और IP लाइसेंस का उपयोग कर सकते हैं।

व्यावहारिक उत्पाद और संभावित कीमतें

अगर निर्माता सॉकेटेबल चिपलेट मॉडल अपनाते हैं तो उपभोक्ता-उन्मुख उत्पाद इस तरह दिख सकते हैं: एक बेसिक फ्रेमवर्क-स्टाइल लैपटॉप या स्मार्टफोन जहां CPU/GPU/NPU चिपलेट सॉकेट-आधारित मॉड्यूल की तरह लगाए जाते हैं। बेस डिवाइस की कीमत वर्तमान मॉडलों के अनुरूप, लगभग 40,000–120,000 रुपये के बीच हो सकती है, जबकि चिपलेट अपग्रेड मॉड्यूल की कीमत उनकी जटिलता पर निर्भर करेगी। उदाहरण के तौर पर, एक ऊर्जा-कुशल CPU चिपलेट $50–$200 (लगभग 4,000–16,000 रुपये) में उपलब्ध हो सकता है, जबकि हाई-एंड GPU या NPU चिपलेट $200–$500 (लगभग 16,000–40,000 रुपये) तक जा सकता है। इन अनुमानों का आधार मौजूदा SoC और मीड-टू-हाई एंड कंपोनेंट्स की कीमतों का औसत तथा पैकेजिंग और परीक्षण लागतों का हिसाब है। बाजार प्रभाव बड़ा होगा: अपग्रेडेबल चिपलेट पारंपरिक रिप्लेसमेंट साइकल को धीमा कर सकते हैं, रीफर्बिशिंग को बढ़ावा दे सकते हैं और उपभोक्ताओं को कस्टमाइज़ेशन के नए विकल्प देंगे।

चुनौतियाँ: थर्मल, सुरक्षा और मानकीकरण

सॉकेटेबल चिपलेट का वादा आकर्षक है, लेकिन कई ठोस बाधाएँ हैं। सबसे पहली चुनौती थर्मल प्रबंधन है: छोटे पैकेज वाले उच्च-प्रदर्शन चिपलेट का हीट सैपरेशन और कूलिंग एक चुनौती है, खासकर स्मार्टफोन जैसे कॉम्पैक्ट फॉर्म-फैक्टर में। दूसरी बड़ी समस्या सुरक्षा और IP प्रोटेक्शन है; अलग-अलग पेटेंट-आधारित ब्लॉक्स को सॉकेट पर रखकर OEM को विश्वसनीय बूट तथा ट्रस्टेड एग्ज़ीक्यूशन सुनिश्चित करना होगा। तीसरी चुनौती मानकीकरण और लाइसेंसिंग की है: अगर हर निर्माता अपना सॉकेट प्रोटोकॉल बनाएगा तो अर्थव्यवस्था बिखर जाएगी। इसलिए उद्योग-स्तर के इंटरकनेक्ट मानक और सिग्नल-इंटीग्रिटी स्पेसिफिकेशंस की जरूरत होगी। अंत में पैकेजिंग और टेस्टिंग लागत हैं; छोटे चिपलेट के कारण फाइनल असेंबली और टेस्टिंग पर नया खर्च आएगा, और बेहतर yields हासिल करने तक कीमतें ऊँची रह सकती हैं।

वर्तमान समाचार और संकेत

पिछले कुछ वर्षों में उद्योग में चिपलेट और मॉड्यूलर पैकेजिंग पर चर्चा बढ़ी है। सर्विस प्रोवाइडरों और बड़े सिलिकॉन डिजाइनरों ने 3D पैकेजिंग और die-to-die इंटरकनेक्ट में निवेश बढ़ाया है। AMD के डेटा-सेंटर हिस्से और कुछ क्लाउड प्लेयर्स ने साबित किया है कि चिपलेट-आधारित मॉडल सक्षम और लागत-कुशल हो सकता है, जबकि कुछ मोबाइल SoC विक्रेताओं ने मल्टी-डाई रूटमैप की तरफ इशारा किया है। छोटी स्टार्टअप भी सॉकेटेबल मॉड्यूल डिजाइन करने में रुचि दिखा रही हैं, खासकर ओपन-हाडवेयर समुदाय में। ये संकेत बताते हैं कि अगले 2–5 वर्षों में उपभोक्ता इलेक्ट्रॉनिक्स में चिपलेट अधिक दिखाई दे सकते हैं, बशर्ते मानक और थर्मल समाधान समय पर आएं।

संभावित प्रभाव: उपयोगकर्ता अनुभव से लेकर उद्योग संरचना तक

सफल सॉकेटेबल चिपलेट इकोसिस्टम उपभोक्ता के लिए तीन बड़े फायदे दे सकता है: कस्टमाइज़ेशन, अपग्रेडेबिलिटी और दीर्घकालिक टिकाऊपन। यूज़र पुराने डिवाइस को पूरी तरह बदलने के बजाय सिर्फ घटक अपग्रेड करके नए फीचर पा सकेंगे। उद्योग के लिए यह मॉडल आपूर्ति श्रृंखला को अधिक मॉड्युलर बनाता है, छोटे फैब्रिकेटर्स और IP डेवलपर्स के लिए अवसर पैदा करता है, और रिपेयर-एंड-रीफर्बिशिंग मार्केट्स को मजबूती देता है। हालांकि OEMs की परंपरागत रिप्लेसमेंट-ड्रिवेन राजस्व संरचनाएँ चुनौतियों में पड़ सकती हैं, और कुछ ब्रांड साझेदारी आधारित मॉडल को अपनाकर नए राजस्व चैनलों पर ध्यान दे सकते हैं।

निष्कर्ष: व्यवहारिकता बनाम कल्पना

सॉकेटेबल चिपलेट एक रोमांचक विचार है जो तकनीकी रीयलिज़्म और बाज़ार दबाव दोनों से प्रोत्साहित हो रहा है। इतिहास बताता है कि जब पैकेजिंग और इंटरकनेक्ट ने बिना व्यवहारिक व्यवधान के काम किया, तब ही बड़े बदलाव हुए हैं। आज भी थर्मल, सुरक्षा, मानकीकरण और लागत जैसी बाधाएँ हैं, पर उद्योग की हालिया गतिविधियाँ और पैकेजिंग तकनीकों में सुधार संकेत देते हैं कि उपभोक्ता-स्तर पर मॉड्यूलर SoC संभव और उपयोगी हो सकता है। अगले कुछ वर्षों में हम देखेंगें कि क्या संकुल मानक बनते हैं, क्या थर्ड-पार्टी मॉड्यूल सफल होते हैं, और क्या यह एक ऐसा मॉडल बनता है जो डिवाइस निर्माण और उपयोगकर्ता अधिकारों दोनों को अधिक लचीला बना दे।